Embedded System Overview.

SoC 是什麼?

SoC (System on Chip) 是一種將整個計算系統整合在單一芯片上的架構,包含多種功能模組。 它是嵌入式系統設計中非常普遍的選擇,因為小小的晶片就幾乎完備了運算系統需要的功能,可謂麻雀雖小五臟俱全。

典型 SoC 包括以下模組:

- CPU: 處理核心,負責執行程式邏輯。

- 內存控制器: 直接管理與 DRAM 的連接。

- 存儲單元: 內建 SRAM 或快閃記憶體,用於存放程式和資料。

- I/O 接口: 如 USB、UART、SPI、I²C 等。

- GPU: 圖形處理器,用於圖形渲染或計算。

- 網絡模組: 支援 WiFi、Ethernet 或 5G。

應用場景包含手機、IoT 裝置、機器人、汽車電子、智慧家居設備等,高通 Snapdragon、Apple A 系列、NVIDIA Tegra 等都是 SoC。

SoC 與 CPU 的差異與比較

CPU 是負責執行程式指令並處理數據的核心計算模組,它是任何計算機系統的主要運算單元。 典型 CPU 包括控制單元 (Control Unit)、算術邏輯單元(ALU)、暫存器(Registers)、快取記憶體 (Cache)。

在嵌入式系統中,CPU 作為 SoC 的一部分,強調一體化,將多個功能模組整合在單一芯片。

- 優勢為:低功耗、低成本、尺寸小、方便。

- 缺點為:由於設計是固定的,升級特定模組的能力有限,靈活性較低、多模組運作可能導致熱量集中的問題。

在個人電腦、伺服器應用,CPU 常是獨立組件,只負責運算,其他功能尚須要其他需要外部模組(如 GPU、I/O 控制器)來組成完整系統,強調性能。

- 優勢為: 性能強、散熱強、擴充性強,因可任意組建並擴充系統。

- 缺點為: 體積大、耗能。

總結是 CPU 是通用的運算核心,可以搭配其他關鍵核心組成像是 PC、伺服器等需要高性能的應用系統。而 CPU 也可以被集成在 SoC 這樣高度整合的系統內,用於功耗敏感、體積有限的設備。

控制硬體裝置的方式就是讀寫其暫存器

硬體裝置的操作主要是通過讀取或寫入裝置的暫存器來實現,這些暫存器為軟體提供了一個與硬體互動的介面。

在 x86 架構中,裝置的暫存器可以被映射到 I/O space(Port-IO) 或 Memory Space(Memory-Mapped I/O, MMIO):

- 被映射到 I/O Space 下的暫存器需使用特殊的指令(如

IN和OUT)來存取。 - 映射到 Memory Space 下的暫存器則可透過一般讀寫記憶體的指令存取。

映射通常由 BIOS 配置,BIOS 在系統啟動時負責初始化硬體,包括列舉和配置 PCI 裝置。對於 PCI 裝置,BIOS 通常會為每個裝置分配資源,比如 I/O Port 空間或 MMIO 空間,並將這些資訊寫入裝置的 PCI Configuration Space 中的相關欄位,例如 Base Address Register (BAR)。

user 需要去查詢裝置暫存器映射的 Base Address,知道地址就能操作裝置的暫存器進而控制裝置。

補充: 在一些嵌入式系統(如 ARM 或 RISC-V 平台)中,裝置通常使用 Memory-Mapped I/O (MMIO),不區分 I/O Space 和 Memory Space。 而如果系統使用的是較新的技術像是 UEFI,則可能由操作系統完成資源分配和配置。

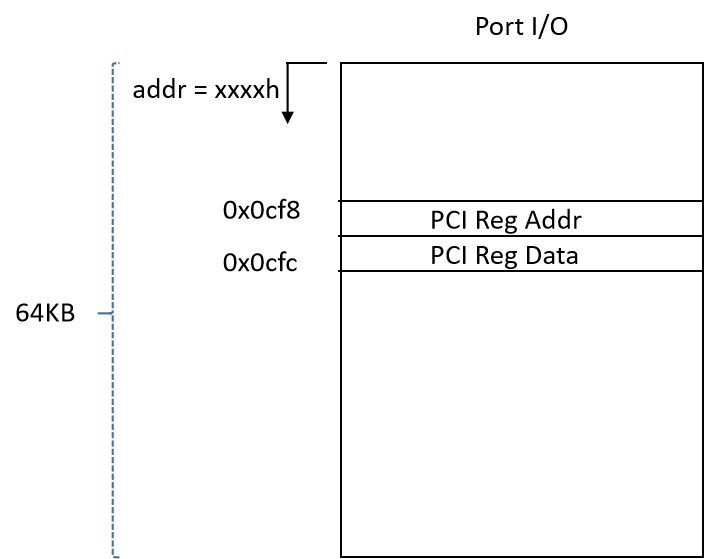

x86 的 I/O space。

這是 x86 架構下 I/O 暫存器的存取介面,透過將周邊裝置之暫存器映射到 I/O Space,就能夠透過讀寫 I/O Space 的方式來控制裝置了。

x86 的 I/O Space 只有 64KB 大小的空間,而且其中許多位址都已保留給特定裝置使用(比如 PCI)。

NB 與 SB 晶片組

北橋 (North Bridge) 的角色

- 高速橋接:NB 是 CPU 與其他高速設備(例如記憶體和 PCI 線路)之間的中介橋。

- 負責連接 CPU 和高速裝置:

- 系統總線管理:負責管理 CPU 與 PCI 總線之間的資料流動。

- 記憶體控制器:負責 CPU 與 DRAM 的連接,處理高速資料傳輸。

- 圖形接口:連接高性能圖形裝置(如 AGP 或 PCIe 的圖形卡)。

南橋 (South Bridge)

- 負責低速裝置的連接,如 ISA、串列埠、並列埠等。

- 通常提供 PCI 到 ISA 的橋接功能。

在傳統的嵌入式或桌上型電腦系統中,CPU 與 NB 是系統架構的核心組件,兩者的關係如下:

- 高速連接:

- 透過前端匯流排(Front-Side Bus, FSB)相連。

- FSB 提供 CPU 與 NB 間的高速資料傳輸通道。

- 共享控制: CPU 通過 NB 控制其他裝置,例如記憶體和外設。

在更現代的設計中,CPU 通常內建記憶體控制器,NB 的角色漸漸由 CPU 整合。此時,PCIe 和其他高速裝置直接與 CPU 連接,而不是經由 NB。

PCI Bus

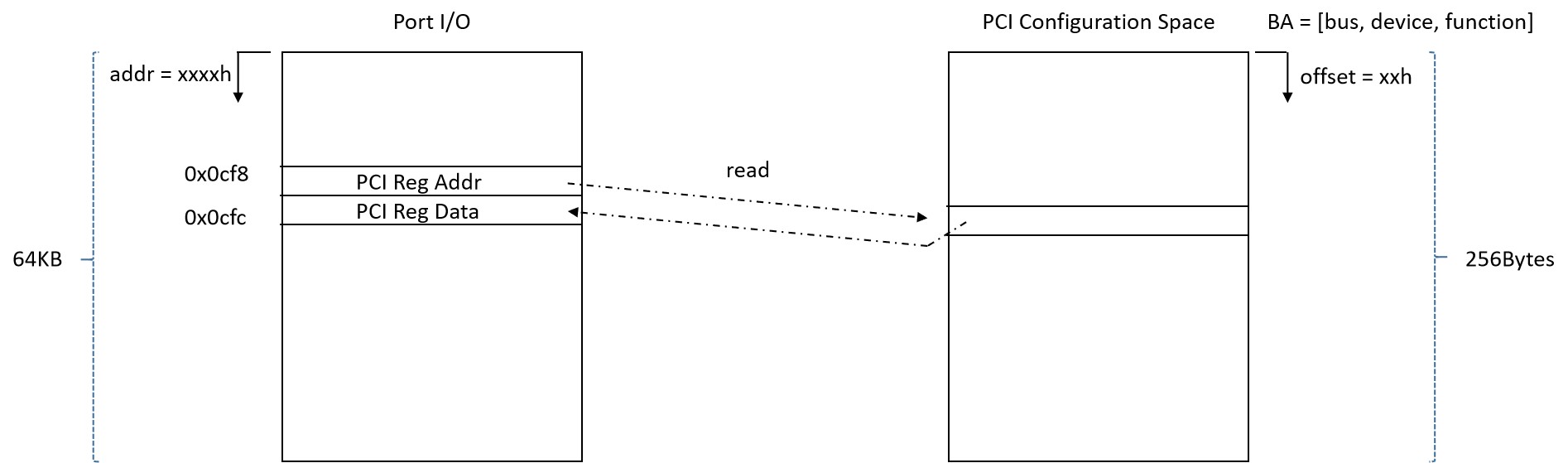

每個 PCI 裝置都有一個標準化的 PCI Configuration Space 用來存放其配置資訊,例如裝置 ID、Vendor ID、BAR (Base Address Register) 等。 裝置之 PCI Configuration Space 的地址由 [bus(8-bit), device(5-bit), function(3-bit)] 決定,再由 offset(8-bit) 決定 PCI 暫存器位址,故每個裝置之 PCI 暫存器空間大小只有 256 Bytes,雖然小但只存放系統配置資訊是夠用的,裝置非 PCI 的暫存器實際上會映射到 I/O Space 或 Memory Space 去。

x86 架構中,在 I/O space 為 PCI 暫存器保留兩個固定位址,作為操作 PCI Configuration Space 的介面。

- 0x0cf8 (4 Bytes) 為 PCI Register Address,由 [bus, device, function, offset] 構成。

- 0x0cfc (4 Bytes) 為 PCI Data,不管是讀取或寫入 PCI 暫存器都是經由這個 I/O space 位址。

讀取 PCI Register:

- user 將目標 PCI Register 地址寫入 I/O space 0x0cf8。

- user 對 I/O space 0x0cfc 進行讀取操作,PCI 就會將暫存器資料寫到 0x0cfc 內返回給 user。

寫入 PCI Register:

- user 將目標 PCI Register 地址寫入 I/O space 0x0cf8。

- user 對 I/O space 0x0cfc 進行寫入操作,PCI 就會將 0x0cfc 的資料存取到暫存器內。

BIOS 在啟動時會掃描所有的 PCI 裝置,為每個裝置分配其暫存器在 I/O Space 或 Memory Space 的映射基底地址,提供操作暫存器的介面。

實現 Pin 腳多工的 Crossbar

SoC 可謂多功能但體積小,物理上的限制使得其腳位數量不足以為所有 SoC 的功能都引出腳位來。 有了 Crossbar 這種切換器,使得腳位可以多工選擇要連接的功能為何,比如說透過設定 Crossbar,我可以選擇 SoC 引腳 Port 5, Pin 3,要使用 GPIO 功能,或者使用 UART Tx 功能。

總之,有了 Crossbar,得以讓 SoC 用戶自己為腳為選擇需要的功能,這讓腳位少但功能豐富的 SoC 足以滿足各種需求。

問題思考:

Q1: 為什麼有些系統使用 PCI-to-PCIe 橋接,將 PCIe 掛載在 PCI 下? 這樣速度較快的 PCIe 不就受限於較慢的 PCI?

確實,將 PCIe 裝置掛在 PCI-to-PCIe 橋接器下,會因為橋接器的設計而受到 PCI 總線速度的限制(如 PCI 的最大傳輸速度為 133 MB/s)。然而,這樣設計並非偶然,而是基於以下原因:

-

向後兼容: 系統需要支援老舊的 PCI 總線設備,同時也想引入現代 PCIe 設備的功能。 某些嵌入式或工業系統需要延續支持舊裝置,但無法完全放棄 PCI 架構。PCI-to-PCIe 橋接提供一個過渡方案,使新型 PCIe 設備能在舊系統中運行。 嵌入式應用中使用 PCI-to-PCIe 來提供特定接口(如 USB、網路等),這樣的作法主要是功能導向而非性能導向,外接的 PCIe 裝置僅需低速數據傳輸。

-

設計成本考量: 使用橋接器比重新設計整個系統更節省成本,如果直接用 PCIe 作為系統總線,將需要修改硬體架構、PCB 佈局,甚至需要開發新驅動。 而橋接器是一種低成本、高兼容性的即刻解決方案。

應用案例

- 嵌入式工業系統: 工業主板使用 PCI-to-PCIe 橋接,允許開發者將舊型 PCI 模組升級為 PCIe 模組,增加壽命。

- 過渡時期主板: 早期 PCIe 系統(如 2000 年代的桌機主板)同時包含 PCI 和 PCIe 插槽,使用 PCI-to-PCIe 橋接來支援 PCIe 顯卡或擴充裝置。

- 混合式嵌入式平台: 工廠中的控制系統同時需要舊有的 PCI 通訊模組和現代化的 PCIe 網路模組,橋接技術便於整合。

橋接器允許一個系統同時支持 PCI 和 PCIe 裝置,這在過渡時期的主板設計中非常常見。 將 PCIe 掛載在 PCI 下雖然限制了 PCIe 的性能,但這樣做的目的是為了兼容性、成本考量,這可能是設計者考量到功能需求多於性能需求,而選擇的一種實用解決方案。如果性能是主要需求,則可能需要考慮升級到完整的 PCIe 架構。